编码

代码对齐风格 格式

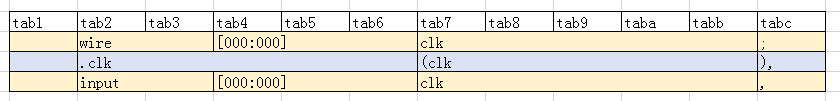

每一行最后一个分号在第12个tab

信号名控制在5个tab内,20bit内

111122223333444455556666777788889999aaaabbbbcccc

信号命名不能超过20B一般2个_

tab1tab2tab3tab4tab5tab6tab7tab8tab9tabatabbtabc

wire [000:000] clk ;

input [000:000] clk ,

input clk ,

.clk (clk ),

always@(posedge clk or posedge rst) begin

if(rst)begin

xx<= #1 'b0;

end else begin

xx<= #1 'b0;

end

end

assign xxx = xxxxxx ;

parameter DLY = 1;

`ifdef SIM_OPEN

parameter IDLE = "IDLE";

parameter IDLE = "IDLE";

reg[127:0] cur_state,next_state;

`else

parameter IDLE = 'd0;

reg[3:0] cur_state,next_state;

`endif

always@(posedge clk or negedge rst_n)begin if(rst_n == 1'b0)begin cur_state <= #DLY IDLE; end else begin cur_state <= #DLY next_state; end end

always@(*)begin

case(cur_state)

IDLE:

begin

if(seq == 2'b1)

next_state = A;

else

next_state = IDLE;

end

default: next_state = IDLE;

endcase

end

状态机相关

确定状态机的状态

假设是人去干,会有哪些步骤,把步骤写出来,就是对应的状态。

明确状态机的输入信号有哪些。输出信号在什么条件下输出。

调试信息:状态机的各个状态用一个寄存器的1bit表示。

上升沿的理解

依据上升沿之前信号的值,在上升沿之前计算出结果,在上升沿时刻更新。

电路的理解

不同状态下,干输出不同的值。

看代码

看代码时,可以将ram,fifo等固定的模块找出,再看其中的逻辑如何操作这些模块。

寄存器定义

要有明确的含义,不能存在歧义。例如表示已发送idle个数,不包含当前idle个数在内

减少状态机的状态个数

采用每个状态内再来一个计数器,计数在这个状态的拍数。----各有利弊