实验目标

来依次看每个断言的时序要求。

实验任务

所有的property assertion都写在接口pkg中,也可以在module,但不能在class中

property p_paddr_no_x;

@(posedge clk) psel |-> !$isunknown(paddr);//指定了clk

//系统函数相当于$countbits(expression, ‘x, ‘z)!=0

//即psel为高时paddr不为x和z

endproperty: p_paddr_no_x

assert property(p_paddr_no_x) else `uvm_error("ASSERT", "PADDR is unknown when PSEL is high")

采样的信号和clk都来自interface

property p_psel_rose_next_cycle_penable_rise;

@(posedge clk) $rose(psel) |=> $rose(penable);

//psel拉高后的下一个clk,penable也拉高

endproperty: p_psel_rose_next_cycle_penable_rise

assert property(p_psel_rose_next_cycle_penable_rise) else `uvm_error("ASSERT", "PENABLE not rose after 1 cycle PSEL rose")

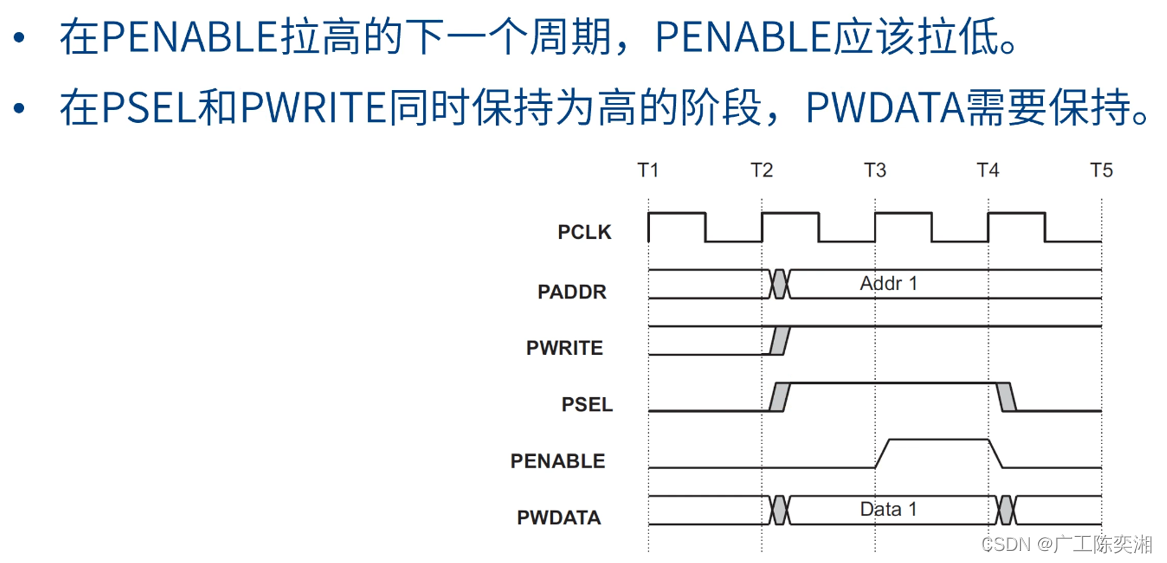

property p_penable_rose_next_cycle_fall;

@(posedge clk) $rose(penable) |=> $fell(penable);

endproperty: p_penable_rose_next_cycle_fall

assert property(p_penable_rose_next_cycle_fall) else `uvm_error("ASSERT", "PENABLE not fall after 1 cycle PENABLE rose")

property p_pwdata_stable_during_trans_phase;

@(posedge clk) ((psel && !penable) ##1 (psel && penable)) |-> $stable(pwdata);

endproperty: p_pwdata_stable_during_trans_phase

assert property(p_pwdata_stable_during_trans_phase) else `uvm_error("ASSERT", "PWDATA not stable during transaction phase")

property p_paddr_stable_until_next_trans;

logic[31:0] addr1, addr2;

@(posedge clk) first_match(($rose(penable),addr1=paddr) ##1 ((psel && !penable)[=1],addr2=$past(paddr))) |-> addr1 == addr2;

endproperty: p_paddr_stable_until_next_trans

assert property(p_paddr_stable_until_next_trans) else `uvm_error("ASSERT", "PADDR not stable until next transaction start")

property p_pwrite_stable_until_next_trans;

logic pwrite1, pwrite2;

@(posedge clk) first_match(($rose(penable),pwrite1=pwrite) ##1 ((psel && !penable)[=1],pwrite2=$past(pwrite))) |-> pwrite1 == pwrite2;

endproperty: p_pwrite_stable_until_next_trans

assert property(p_pwrite_stable_until_next_trans) else `uvm_error("ASSERT", "PWRITE not stable until next transaction start")

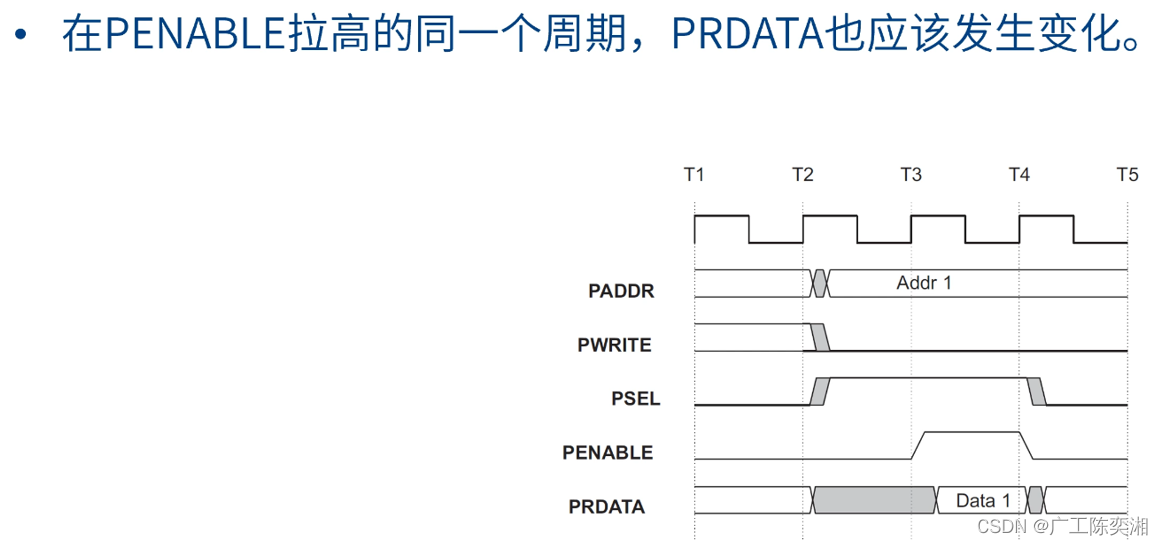

property p_prdata_available_once_penable_rose;

@(posedge clk) $rose(penable) && !pwrite |-> !$stable(prdata);

endproperty: p_prdata_available_once_penable_rose

assert property(p_prdata_available_once_penable_rose) else `uvm_error("ASSERT", "PRDATA not available once PENABLE rose")

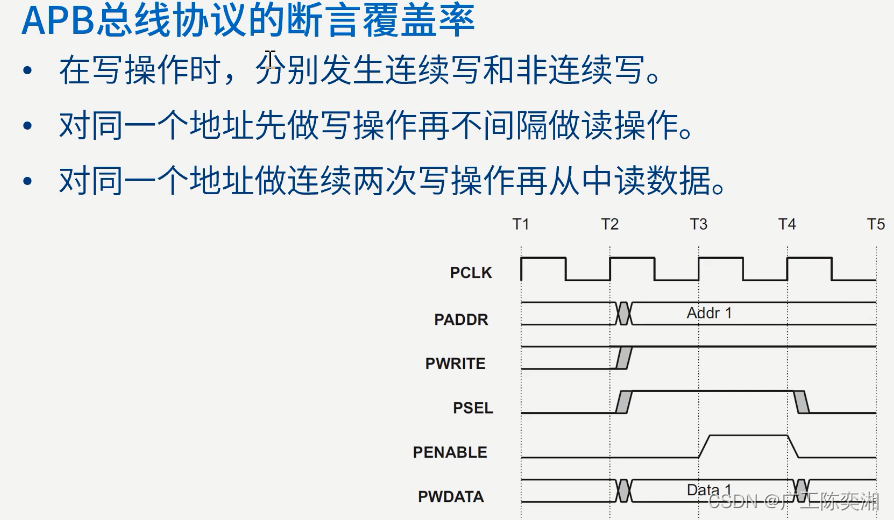

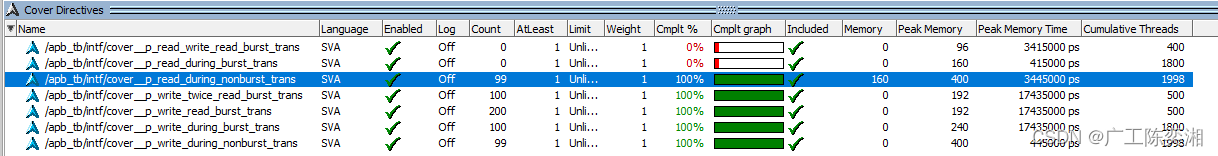

然后是断言覆盖率。

连续写和非连续写。

连续写,enable拉高后,写第一个是sel ##1 enable,然后马上sel ##1 enable

非连续写时,enable拉高后,write贯穿整个写的过程,enable连续2个clk为低(和连续写区分),1个clk后enable为高。

property p_write_during_nonburst_trans;

@(posedge clk) $rose(penable) |-> pwrite throughout (##1 (!penable)[*2] ##1 penable[=1]);

endproperty: p_write_during_nonburst_trans

cover property(p_write_during_nonburst_trans);

property p_write_during_burst_trans;

@(posedge clk) $rose(penable) |-> pwrite throughout (##2 penable);

endproperty: p_write_during_burst_trans

cover property(p_write_during_burst_trans);对同一地址先写后读,也就是连续的。

enable拉高后,write为高,地址给到变量存起来,然后准备读,2个clk后enable拉高,write拉低,把地址给到变量,要求两次的地址相同

property p_write_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && pwrite, addr=paddr) |-> (##2 ($rose(penable) && !pwrite && addr==paddr));

endproperty: p_write_read_burst_trans

cover property(p_write_read_burst_trans);同一地址连续写两次后读。

这是验证需要激励发生的测试

property p_write_twice_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && pwrite, addr=paddr) |-> (##2 ($rose(penable) && pwrite && addr==paddr) ##2 ($rose(penable) && !pwrite && addr==paddr) );

endproperty: p_write_twice_read_burst_trans

cover property(p_write_twice_read_burst_trans);

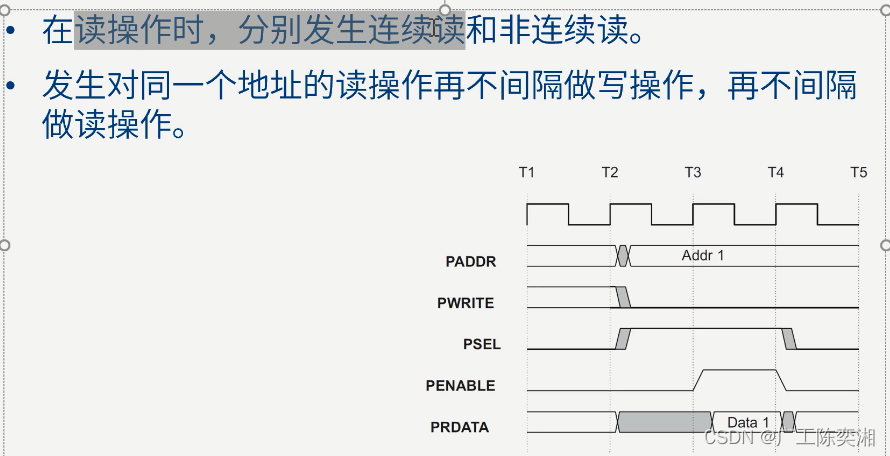

连续读和非连续读:write一直为低

property p_read_during_nonburst_trans;

@(posedge clk) $rose(penable) |-> !pwrite throughout (##1 (!penable)[*2] ##1 penable[=1]);

endproperty: p_read_during_nonburst_trans

cover property(p_read_during_nonburst_trans);

property p_read_during_burst_trans;

@(posedge clk) $rose(penable) |-> !pwrite throughout (##2 penable);

endproperty: p_read_during_burst_trans

cover property(p_read_during_burst_trans);对同一地址连续的读写读

property p_read_write_read_burst_trans;

logic[31:0] addr;

@(posedge clk) ($rose(penable) && !pwrite, addr=paddr) |-> (##2 ($rose(penable) && pwrite && addr==paddr) ##2 ($rose(penable) && !pwrite && addr==paddr) );

endproperty: p_read_write_read_burst_trans

cover property(p_read_write_read_burst_trans);要求property短一点,名字显示出操作。不行就得加注释,注明检查的协议、覆盖的激励时序。

外部设计控制assertion

initial begin: assertion_control

fork

forever begin

wait(rstn == 0);

$assertoff();

wait(rstn == 1);

$asserton();

end

join_none

end仿真

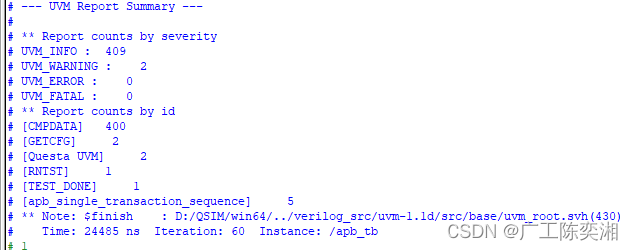

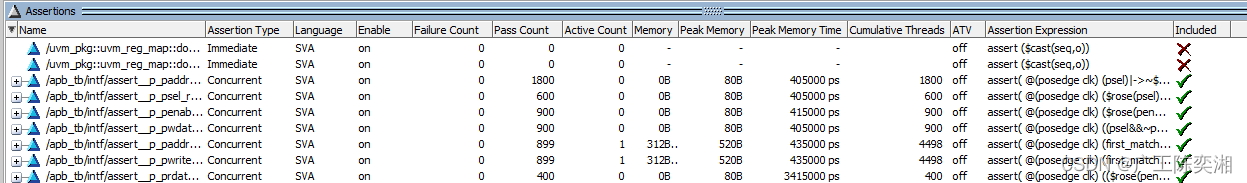

尽管这里没有error,但是assertion并不一定没有问题,得看trigger了没有

view-coverage-assertion

两个uvm内置的立即断言忽略。其他自定义的,failure count为0(前置seq满足,后置seq不满足),说明真的成功了,pass count为触发的次数(前置seq满足,后置seq也满足)

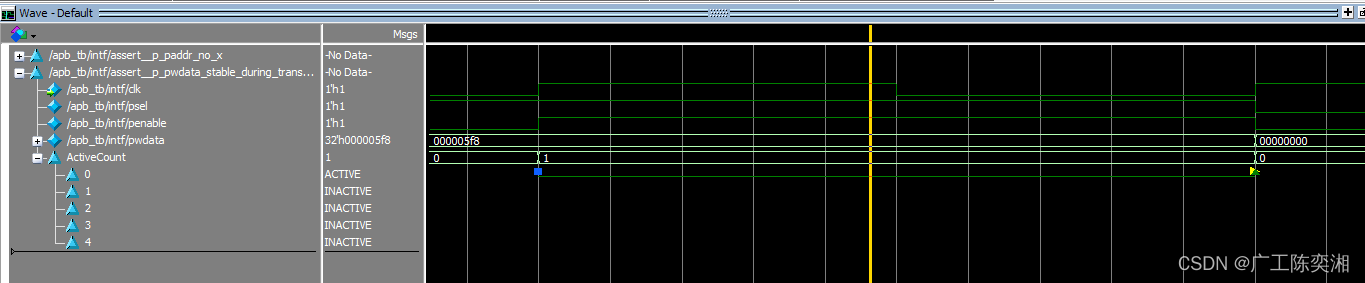

右键assertion可以add wave,看具体波形

activecount一共有三种颜色,对应蓝色start、active、inactive、pass

0-4表示交叠的个数

断言覆盖率。