问题描述

我想在参数语句中实现一些复杂的计算,但这会使我的代码难以阅读。我知道其他一些FPGA工程师使用“函数”来实现。代码如下所示:

function integer calc_head_len;

input [11:0] DFF;

begin

calc_head_len=0;

if(DFF[11]) calc_head_len=calc_head_len + 16;

if(DFF[10]) calc_head_len=calc_head_len + SFL_WIDTH;

if(DFF[9]) calc_head_len=calc_head_len + FDSTI_WIDTH_PORT;

if(DFF[8]) calc_head_len=calc_head_len + FDSSI_WIDTH_PORT;

if(DFF[7]) calc_head_len=calc_head_len + BN_WIDTH;

end

endfunction

localparam FRAME_HEAD_LEN=calc_head_len(DFF);

问题是,首先,据我所知,“参数”赋值仅应使用常量表达式,而“函数”可以计算变量,那么为什么可以?

第二,“参数”不会占用逻辑资源,因为它们可以在合成阶段进行计算,但是“功能”是否可以同时计算?否则会占用额外的资源?

感谢帮助!

解决方法

如果函数的参数仅是常量或参数,而函数的返回值仅取决于这些参数,则该工具会将返回值传播为另一个常量。这样就不会占用任何额外的资源。

设置时间 控制面板

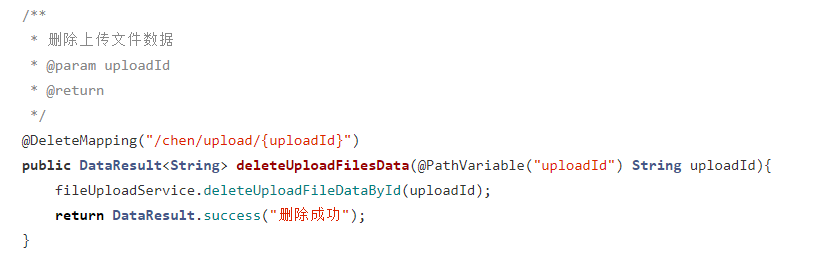

设置时间 控制面板 错误1:Request method ‘DELETE‘ not supported 错误还原:...

错误1:Request method ‘DELETE‘ not supported 错误还原:...