问题描述

我是VHDL的新手。我正在尝试为Xilinx FPGA上的矢量点或标量积设计通用代码。假设我们有一个向量,两个向量

V1=[1,4,5,1] and V2=[3,6,9,1].

我们可以使用

找到它V1.V2=(1x3)+(4x6)+(5x9)+(1x1)=73

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.numeric_std.ALL;

entity dot_product is

Port ( vector_x : in STD_LOGIC_VECTOR (3 downto 0);

vector_y : in STD_LOGIC_VECTOR (3 downto 0);

r0 : out STD_LOGIC_VECTOR (3 downto 0);

r1 : out STD_LOGIC_VECTOR (3 downto 0);

r2 : out STD_LOGIC_VECTOR (3 downto 0);

result : out STD_LOGIC_VECTOR (7 downto 0));

end dot_product;

architecture Behavioral of dot_product is

begin

r0 <= std_logic_vector(signed(vector_x(0)* vector_y(0)));

r1 <= std_logic_vector(signed(vector_x(1)* vector_y(1)));

r2 <= std_logic_vector(signed(vector_x(2)* vector_y(2)));

r3 <= std_logic_vector(signed(vector_x(3)* vector_y(3)));

result<=r0+r1+r2+r3;

end Behavioral;

我们如何在VHDL中找到其点积,后来我可以根据需要更改矢量大小。请帮忙。谢谢:)

解决方法

这些是一些注意事项:

- vector_x:位于STD_LOGIC_VECTOR中(3到0);

这不是数学中的向量。它是一个由零和一的比特组成的数组。因此您可以使用它来表示0(0000)到15(1111)之间的数字。

如果您想要一个向量,请考虑声明一个std_logic_vector数组。

类型t_vector是std_logic_vector的数组(整数范围)(3至0);

考虑阅读以下内容:https://www.nandland.com/vhdl/examples/example-array-type-vhdl.html

然后将向量声明为类型为t_vector的数组。

之后,可以在进程中使用for循环进行乘法和加法。 考虑阅读以下内容:http://habeebq.github.io/writing-a-2x2-matrix-multiplier-in-vhdl.html

要具有通用数组大小,请考虑使用不受限制的数组或通用数组作为大小。

entity dot_product is

generic (width : positive := 8);

port (vector_x : in t_vector (width downto 0);

vector_y : in t_vector (width downto 0);

result : out STD_LOGIC_VECTOR (7 downto 0));

end dot_product ;

设置时间 控制面板

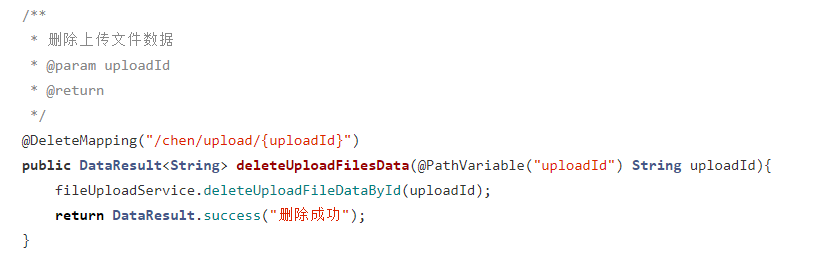

设置时间 控制面板 错误1:Request method ‘DELETE‘ not supported 错误还原:...

错误1:Request method ‘DELETE‘ not supported 错误还原:...