问题描述

美好的一天!我有以下问题:

我正在使用Xilinx ISE 14.5设计Spartan 6 FPGA。我注意到这是我的设计之一,我无法更改信号的物理引脚映射。当我将.ucf文件中的行更改为另一个物理引脚时,重新合成并重新实现了设计并上传了新的.bit文件,实际信号仍然被路由到旧引脚。

此后,我完全清除了.ucf文件,然后再次运行综合,实现等操作,该软件甚至没有向我发出有关丢失的引脚声明的警告。

这是我的代码:

entity top is

port(

i_clk : IN STD_LOGIC;

o_test3 : INOUT STD_LOGIC := '1'

);

end top;

architecture Behavioral of top is

begin

p_test: process (i_clk) begin

if rising_edge(i_clk) then

o_test3 <= not o_test3;

end if;

end process;

end Behavioral;

enter code here

.ucf文件完全为空。我希望该软件会引发有关i_clk和o_test3缺少声明的警告。我的理解错了吗?

如果它应该发出警告,这是否是可以帮助解决的错误?我正在考虑安装14.7版本,希望可以解决此问题,但是我想先问一下所有可能的解决方案。预先感谢。

解决方法

如果在UCF文件中未提供引脚的LOC约束,则ISE将选择该引脚的位置。我不记得它是否提供警告。

14.7与14.5的差别很小,因此升级不会改变您的情况。

没有UCF文件,我们不能真正帮助您解决为什么不遵守LOC约束的情况。

设置时间 控制面板

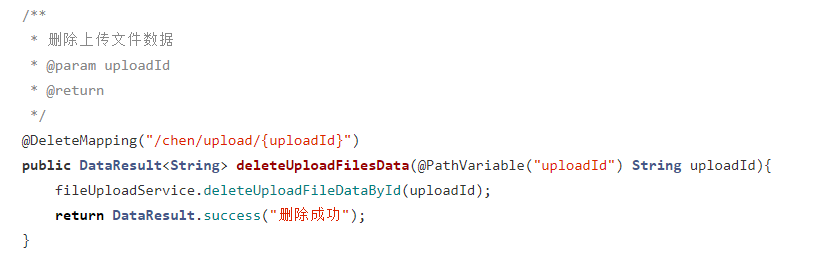

设置时间 控制面板 错误1:Request method ‘DELETE‘ not supported 错误还原:...

错误1:Request method ‘DELETE‘ not supported 错误还原:...