问题描述

假设我正在使用xilinx Vivado,并使用以下verilog代码,并使用插入模块将其插入到块设计中:

module vivado_amm_ip #(

parameter lw = 8,parameter aw = 32,parameter dw = 64

) (

// Avalon Master

/*Synchrnous Reset Output To Avalon */

output wire m_amm_aresetn,/* Clock Output To Avalon ............................................*/

output wire m_amm_aclk,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm ADDRESS" *)

output reg [aw-1:0] m_amm_addr,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm WRITE" *)

output reg m_amm_wen,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm WRITEDATA" *)

output reg [dw-1:0] m_amm_wdata,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm WAITREQUEST" *)

input wire m_amm_wait,//unused

(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm READ" *)

output wire m_amm_ren,//unused

(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm READDATA" *)

input wire [dw-1:0] m_amm_rdata,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm READDATAVALID" *)

input wire m_amm_rvalid,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm BEGINBURSTTRANSFER" *)

output wire m_amm_bstart,//unused

(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 m_amm BURSTCOUNT" *)

output wire [lw-1:0] m_amm_bcount,//unused

);

endmodule

当我将设计重新加载到vivado时,我总是收到以下错误消息:

[IP_Flow 19-4751] Bus Interface 'm_amm_aclk': FREQ_HZ bus parameter is missing for output clock interface.

在verilog中推断amm avalon总线端口时,如何摆脱臭名昭著的Vivado FREQ_HZ丢失错误?

我应该在amm时钟信号上方的模块中放入某种类型的属性标签吗?不?

但是,我可以在Vivado的文档中找到有关如何为amm端口添加此属性的信息...

解决方法

基于EML的答案:

`timescale 1ns/10ps

module vivado_amm_core (

(* X_INTERFACE_INFO = "xilinx.com:signal:clock:1.0 s_axi_aclk CLK" *)

input logic s_axi_aclk,(* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME s_axi_aresetn,POLARITY ACTIVE_LOW,INSERT_VIP 0" *)

(* X_INTERFACE_INFO = "xilinx.com:signal:reset:1.0 s_axi_aresetn RST" *)

input logic s_axi_aresetn,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON ADDRESS" *)

output logic [31:0] avm_address,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON WRITE" *)

output logic avm_write,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON READ" *)

output logic avm_read,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON BYTEENABLE" *)

output logic [3:0] avm_byteenable,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON WRITEDATA" *)

output logic [31:0] avm_writedata,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON READDATA" *)

input logic [31:0] avm_readdata,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON RESPONSE" *)

input logic [1:0] avm_resp,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON READDATAVALID" *)

input logic avm_readdatavalid,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON WRITERESPONSEVALID" *)

input logic avm_writeresponsevalid,(* X_INTERFACE_INFO = "xilinx.com:interface:avalon:1.0 M_AVALON WAITREQUEST" *)

input logic avm_waitrequest

(* X_INTERFACE_PARAMETER = "XIL_INTERFACENAME s_axi_aclk,ASSOCIATED_BUSIF M_AVALON,ASSOCIATED_RESET s_axi_aresetn,FREQ_HZ 100000000,FREQ_TOLERANCE_HZ 0,PHASE 0.000,INSERT_VIP 0" *)

);

/*insert logic*/

endmodule

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

entity vivado_amm_core is

port (

s_amm_aclk :in std_logic;

s_amm_aresetn :in std_logic;

s_amm_wait :out std_logic;

s_amm_bstart :in std_logic;

s_amm_bcount :in std_logic_vector(m_axi_lw-1 downto 0);

s_amm_blast :in std_logic;

s_amm_addr :in std_logic_vector(m_axi_aw-1 downto 0);

s_amm_ren :in std_logic;

s_amm_rdata :out std_logic_vector(m_axi_dw-1 downto 0);

s_amm_rvalid :out std_logic;

s_amm_wen :in std_logic;

s_amm_wdata :in std_logic_vector(m_axi_dw-1 downto 0);

);

end entity;

architecture rtl of amm_core is

-- X_INTERFACE_INFO Attribute only works in ghdl if compiled as

-- "ghdl.exe -a -frelaxed-rules --std=08 --ieee=synopsys ..."

-- only need this declaration once per multiple interfaces...

ATTRIBUTE X_INTERFACE_INFO :STRING;

ATTRIBUTE X_INTERFACE_PARAMETER :STRING;

attribute X_INTERFACE_INFO of s_amm_aclk :signal is "xilinx.com:signal:clock:1.0 s_amm_clk CLK";

attribute X_INTERFACE_INFO of s_amm_aresetn :signal is "xilinx.com:signal:clock:1.0 s_amm_aresetn RST";

ATTRIBUTE X_INTERFACE_PARAMETER of s_amm_aclk :SIGNAL is "ASSOCIATED_BUSIF s_amm,ASSOCIATED_RESET s_amm_aresetn,FREQ_HZ 100000000";

attribute X_INTERFACE_INFO of s_amm_wait :signal is "xilinx.com:interface:avalon:1.0 s_amm WAITREQUEST";

attribute X_INTERFACE_INFO of s_amm_addr :signal is "xilinx.com:interface:avalon:1.0 s_amm ADDRESS";

attribute X_INTERFACE_INFO of s_amm_ren :signal is "xilinx.com:interface:avalon:1.0 s_amm READ";

attribute X_INTERFACE_INFO of s_amm_rdata :signal is "xilinx.com:interface:avalon:1.0 s_amm READDATA";

attribute X_INTERFACE_INFO of s_amm_rvalid :signal is "xilinx.com:interface:avalon:1.0 s_amm READDATAVALID";

attribute X_INTERFACE_INFO of s_amm_wen :signal is "xilinx.com:interface:avalon:1.0 s_amm WRITE";

attribute X_INTERFACE_INFO of s_amm_wdata :signal is "xilinx.com:interface:avalon:1.0 s_amm WRITEDATA";

attribute X_INTERFACE_INFO of s_amm_bstart :signal is "xilinx.com:interface:avalon:1.0 s_amm BEGINBURSTTRANSFER";

attribute X_INTERFACE_INFO of s_amm_bcount :signal is "xilinx.com:interface:avalon:1.0 s_amm BURSTCOUNT";

begin

end architecuture;

module bd_axicore_pcie(

//====================================================================

// Verilo-2001 MACROS to Define Vivado Block Design Interfaces

//====================================================================

// PCIe Core Clock

`define hz_pcie 62500000

// ZYNQ Fast Clock

`define hz_sys 50000000

//(NOTE: no spaces allowed after backslash lines continuation)

// INPUT CLOCK,with inteface

`define k(name_clock,name_reset,name_interface) \

(* X_INTERFACE_INFO = `"xilinx.com:signal:clock:1.0 name_clock CLK`" *) \

(* X_INTERFACE_PARAMETER = `"XIL_INTERFACENAME name_clock,ASSOCIATED_BUSIF name_interface,ASSOCIATED_RESET name_reset `" *)

// OUTPUT CLOCK,with interface

`define c(name_clock,freq_hz,ASSOCIATED_RESET name_reset,FREQ_HZ freq_hz `" *)

// OUTPUT CLOCK,no Interface

`define z(name_clock,freq_hz) \

(* X_INTERFACE_INFO = `"xilinx.com:signal:clock:1.0 name_clock CLK`" *) \

(* X_INTERFACE_PARAMETER = `"ASSOCIATED_RESET name_reset,FREQ_HZ freq_hz `" *)

// INPUT CLOCK,no Interface

`define v(name_clock,name_reset) \

(* X_INTERFACE_INFO = `"xilinx.com:signal:clock:1.0 name_clock CLK`" *) \

(* X_INTERFACE_PARAMETER = `"ASSOCIATED_RESET name_reset `" *)

// map signal as interface reset

`define r(name_reset) \

(* X_INTERFACE_INFO = `"xilinx.com:signal:reset:1.0 name_reset RST `" *) \

(* X_INTERFACE_PARAMETER = `"POLARITY ACTIVE_LOW`" *)

// map signal to interface

`define x(name_iterface,name_item) \

(* X_INTERFACE_INFO = `"xilinx.com:interface:aximm:1.0 name_iterface name_item `" *)

// map signal to interface

`define y(name_iterface,name_item) \

(* X_INTERFACE_INFO = `"xilinx.com:interface:avalon:1.0 name_iterface name_item `" *)

//====================================================================

// ZYNQ Fast Clock

//====================================================================

input wire fclk_clk,output wire fclk_rstn,//====================================================================

// FPGA IO

//====================================================================

// LED's

output wire [2:0] pad_led_row,// Video In

input wire pad_vin_clk,input wire pad_vin_hs,input wire pad_vin_vs,input wire [23:0] pad_vin_rgb,// Testbench Signals

output wire pad_vidbuf_enabled,output wire [7:0] pad_vidbuf_mode,// I2C for PizoZed Board

inout wire pad_brd_scl,inout wire pad_brd_sda,//====================================================================

// PCIE: Clock / reset

//====================================================================

input wire i_pcie_core_linkup,//====================================================================

// PCIE: Status

//====================================================================

input wire i_pcie_interrupt,output wire o_pcie_stat_configured,output wire o_pcie_stat_linkup,//=================================================================================

// ARTIX AVALON PORT

//=================================================================================

`y(s_amm_atx,WAITREQUEST) output wire s_amm_atx_wait,`y(s_amm_atx,ADDRESS) input wire [31:0] s_amm_atx_addr,WRITE) input wire s_amm_atx_wen,WRITEDATA) input wire [31:0] s_amm_atx_wdata,READ) input wire s_amm_atx_ren,READDATA) output wire [31:0] s_amm_atx_rdata,READDATAVALID) output wire s_amm_atx_rvalid,//=================================================================================

// "Zynq General Purpose" Bus (AXI-LITE)

//=================================================================================

`x(s_axi_zgp,AWADDR) input wire [31:0] s_axi_zgp_awaddr,`x(s_axi_zgp,AWPROT) input wire [2:0] s_axi_zgp_awprot,AWVALID) input wire s_axi_zgp_awvalid,AWREADY) output wire s_axi_zgp_awready,WDATA) input wire [31:0] s_axi_zgp_wdata,WVALID) input wire s_axi_zgp_wvalid,WREADY) output wire s_axi_zgp_wready,WSTRB) input wire [3:0] s_axi_zgp_wstrb,BRESP) output wire [1:0] s_axi_zgp_bresp,WVALID) output wire s_axi_zgp_bvalid,BREADY) input wire s_axi_zgp_bready,ARADDR) input wire [31:0] s_axi_zgp_araddr,ARPROT) input wire [2:0] s_axi_zgp_arprot,ARVALID) input wire s_axi_zgp_arvalid,ARREADY) output wire s_axi_zgp_arready,RDATA) output wire [31:0] s_axi_zgp_rdata,RRESP) output wire [1:0] s_axi_zgp_rresp,RVALID) output wire s_axi_zgp_rvalid,RREADY) input wire s_axi_zgp_rready,//=================================================================================

// PCIE: CTL

//=================================================================================

`x(m_axi_pcie_ctl,ARADDR) output wire [31:0] m_axi_pcie_ctl_araddr,`x(m_axi_pcie_ctl,ARREADY) input wire m_axi_pcie_ctl_arready,ARVALID) output wire m_axi_pcie_ctl_arvalid,AWADDR) output wire [31:0] m_axi_pcie_ctl_awaddr,AWREADY) input wire m_axi_pcie_ctl_awready,AWVALID) output wire m_axi_pcie_ctl_awvalid,BREADY) output wire m_axi_pcie_ctl_bready,BRESP) input wire [1:0] m_axi_pcie_ctl_bresp,BVALID) input wire m_axi_pcie_ctl_bvalid,RDATA) input wire [31:0] m_axi_pcie_ctl_rdata,RREADY) output wire m_axi_pcie_ctl_rready,RRESP) input wire [1:0] m_axi_pcie_ctl_rresp,RVALID) input wire m_axi_pcie_ctl_rvalid,WDATA) output wire [31:0] m_axi_pcie_ctl_wdata,WREADY) input wire m_axi_pcie_ctl_wready,WSTRB) output wire [3:0] m_axi_pcie_ctl_wstrb,WVALID) output wire m_axi_pcie_ctl_wvalid,//=================================================================================

// PCIE: DT0

//=================================================================================

`x(m_axi_pcie_dt0,ARADDR) output wire [31:0] m_axi_pcie_dt0_araddr,`x(m_axi_pcie_dt0,ARBURST) output wire [1:0] m_axi_pcie_dt0_arburst,ARID) output wire [3:0] m_axi_pcie_dt0_arid,ARLEN) output wire [7:0] m_axi_pcie_dt0_arlen,ARREADY) input wire m_axi_pcie_dt0_arready,ARREGION) output wire [3:0] m_axi_pcie_dt0_arregion,ARSIZE) output wire [2:0] m_axi_pcie_dt0_arsize,ARVALID) output wire m_axi_pcie_dt0_arvalid,AWADDR) output wire [31:0] m_axi_pcie_dt0_awaddr,AWBURST) output wire [1:0] m_axi_pcie_dt0_awburst,AWID) output wire [3:0] m_axi_pcie_dt0_awid,AWLEN) output wire [7:0] m_axi_pcie_dt0_awlen,AWREADY) input wire m_axi_pcie_dt0_awready,AWREGION) output wire [3:0] m_axi_pcie_dt0_awregion,AWSIZE) output wire [2:0] m_axi_pcie_dt0_awsize,AWVALID) output wire m_axi_pcie_dt0_awvalid,BID) input wire [3:0] m_axi_pcie_dt0_bid,BREADY) output wire m_axi_pcie_dt0_bready,BRESP) input wire [1:0] m_axi_pcie_dt0_bresp,BVALID) input wire m_axi_pcie_dt0_bvalid,RDATA) input wire [63:0] m_axi_pcie_dt0_rdata,RID) input wire [3:0] m_axi_pcie_dt0_rid,RLAST) input wire m_axi_pcie_dt0_rlast,RREADY) output wire m_axi_pcie_dt0_rready,RRESP) input wire [1:0] m_axi_pcie_dt0_rresp,RVALID) input wire m_axi_pcie_dt0_rvalid,WDATA) output wire [63:0] m_axi_pcie_dt0_wdata,WLAST) output wire m_axi_pcie_dt0_wlast,WREADY) input wire m_axi_pcie_dt0_wready,WSTRB) output wire [7:0] m_axi_pcie_dt0_wstrb,WVALID) output wire m_axi_pcie_dt0_wvalid,//=================================================================================

// PCIE: DT1

//=================================================================================

`x(s_axi_pcie_dt1,ARADDR) input wire [31:0] s_axi_pcie_dt1_araddr,`x(s_axi_pcie_dt1,ARBURST) input wire [1:0] s_axi_pcie_dt1_arburst,ARCACHE) input wire [3:0] s_axi_pcie_dt1_arcache,ARLEN) input wire [7:0] s_axi_pcie_dt1_arlen,ARLOCK) input wire s_axi_pcie_dt1_arlock,ARPROT) input wire [2:0] s_axi_pcie_dt1_arprot,ARREADY) output wire s_axi_pcie_dt1_arready,ARSIZE) input wire [2:0] s_axi_pcie_dt1_arsize,ARVALID) input wire s_axi_pcie_dt1_arvalid,AWADDR) input wire [31:0] s_axi_pcie_dt1_awaddr,AWBURST) input wire [1:0] s_axi_pcie_dt1_awburst,AWCACHE) input wire [3:0] s_axi_pcie_dt1_awcache,AWLEN) input wire [7:0] s_axi_pcie_dt1_awlen,AWLOCK) input wire s_axi_pcie_dt1_awlock,AWPROT) input wire [2:0] s_axi_pcie_dt1_awprot,AWREADY) output wire s_axi_pcie_dt1_awready,AWSIZE) inout wire [2:0] s_axi_pcie_dt1_awsize,AWVALID) input wire s_axi_pcie_dt1_awvalid,BREADY) input wire s_axi_pcie_dt1_bready,BRESP) output wire [1:0] s_axi_pcie_dt1_bresp,BVALID) output wire s_axi_pcie_dt1_bvalid,RDATA) output wire [63:0] s_axi_pcie_dt1_rdata,RLAST) output wire s_axi_pcie_dt1_rlast,RREADY) input wire s_axi_pcie_dt1_rready,RRESP) output wire [1:0] s_axi_pcie_dt1_rresp,RVALID) output wire s_axi_pcie_dt1_rvalid,WDATA) input wire [63:0] s_axi_pcie_dt1_wdata,WLAST) input wire s_axi_pcie_dt1_wlast,WREADY) output wire s_axi_pcie_dt1_wready,WSTRB) input wire [7:0] s_axi_pcie_dt1_wstrb,WVALID) input wire s_axi_pcie_dt1_wvalid,//=================================================================================

// Clocks & Resets

//=================================================================================

`r(s_axi_zgp_rstn) output wire s_axi_zgp_rstn,`r(s_amm_atx_rstn) output wire s_amm_atx_rstn,`r(i_pcie_core_rstn) input wire i_pcie_core_rstn,`define buses m_axi_pcie_dt0:s_axi_pcie_dt1:m_axi_pcie_ctl

`c(s_axi_zgp_clk,s_axi_zgp_rstn,`hz_sys,s_axi_zgp) output wire s_axi_zgp_clk,`c(s_amm_atx_clk,s_amm_atx_rstn,s_amm_atx) output wire s_amm_atx_clk,`k(i_pcie_core_clk,i_pcie_core_rstn,`buses) input wire i_pcie_core_clk

`undef buses

`undef k

`undef c

`undef z

`undef v

`undef r

`undef x

`undef y

`undef hz_pcie

`undef hz_sys

);

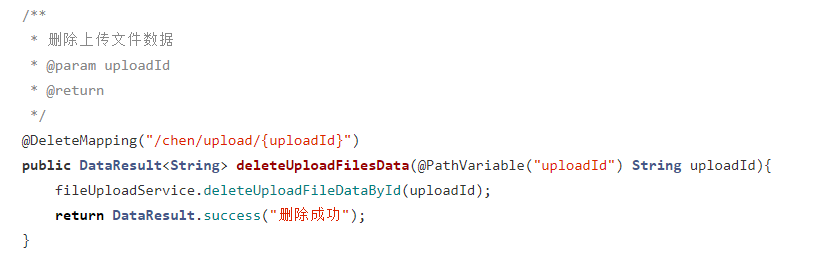

设置时间 控制面板

设置时间 控制面板 错误1:Request method ‘DELETE‘ not supported 错误还原:...

错误1:Request method ‘DELETE‘ not supported 错误还原:...