问题描述

我正在尝试使用VecInit()like it声明一个«rom»:

val GbColors = VecInit(Array(GB_GREEN0,GB_GREEN1,GB_GREEN2,GB_GREEN3))

以GB_GREENx声明为:

class VgaColors extends Bundle {

val red = UInt(6.W)

val green = UInt(6.W)

val blue = UInt(6.W)

}

//...

object GbConst {

//...

/* "#9BBC0F"*/

val GB_GREEN0 = (new VgaColors()).Lit(_.red -> "h26".U(6.W),_.green -> "h2F".U(6.W),_.blue -> "h03".U(6.W))

/* "#8BAC0F"*/

val GB_GREEN1 = (new VgaColors()).Lit(_.red -> "h1E".U(6.W),_.green -> "h27".U(6.W),_.blue -> "h03".U(6.W))

/* "#306230"*/

val GB_GREEN2 = (new VgaColors()).Lit(_.red -> "h0C".U(6.W),_.green -> "h18".U(6.W),_.blue -> "h0C".U(6.W))

/*"#0F380F"*/

val GB_GREEN3 = (new VgaColors()).Lit(_.red -> "h03".U(6.W),_.green -> "h0E".U(6.W),_.blue -> "h03".U(6.W))

我无法将GbColors用作indexable Vec:

io.vga_color := GbColors(io.mem_data)

它会生成Java堆栈错误:

[info] [0.004] Elaborating design...

[error] chisel3.internal.ChiselException: Connection between sink (VgaColors(IO in unelaborated MemVga)) and source (VgaColors(Wire in GbWrite)) failed @.blue: Sink or source unavailable to current module.

[error] ...

[error] at gbvga.MemVga.$anonfun$new$42(memvga.scala:87)

[error] at scala.runtime.java8.JFunction0$mcV$sp.apply(JFunction0$mcV$sp.java:23)

[error] at chisel3.WhenContext.<init>(When.scala:80)

[error] at chisel3.when$.apply(When.scala:32)

[error] at gbvga.MemVga.<init>(memvga.scala:86)

[error] at gbvga.GbVga.$anonfun$memvga$1(gbvga.scala:24)

[error] at chisel3.Module$.do_apply(Module.scala:54)

[error] at gbvga.GbVga.<init>(gbvga.scala:24)

[error] at gbvga.GbVgaDriver$.$anonfun$new$9(gbvga.scala:53)

[error] ... (Stack trace trimmed to user code only,rerun with --full-stacktrace if you wish to see the full stack trace)

...

要管理它,我必须使用switch(){is()}格式:

switch(io.mem_data) {

is("b00".U) {

io.vga_color := GB_GREEN0

}

is("b01".U) {

io.vga_color := GB_GREEN1

}

is("b10".U) {

io.vga_color := GB_GREEN2

}

is("b11".U) {

io.vga_color := GB_GREEN3

}

}

但是我认为它太冗长了。 我的VecInit()«rom»有什么问题?

[编辑]

我的版本是:

$ java -version

java version "1.8.0_151"

Java(TM) SE Runtime Environment (build 1.8.0_151-b12)

Java HotSpot(TM) 64-Bit Server VM (build 25.151-b12,mixed mode)

$ scala -version

Scala code runner version 2.11.7-20150420-135909-555f8f09c9 -- Copyright 2002-2013,LAMP/EPFL

在build.sbt中:

val defaultVersions = Map(

"chisel3" -> "3.4.0-RC1","chisel-iotesters" -> "1.5.0-RC1","chisel-formal" -> "0.1-SNAPSHOT",)

解决方法

我认为这里的问题是因为Bundle中的GbConst是在Module之外创建的。一种可能的解决方法是使GbConst成为trait,并将其添加到需要访问这些值的模块中。 (我创建了一个PR,尽管它可能创建了很多Bundles副本,但似乎表明该方法有效。)另一种方法(我没有尝试过)是创建一个模块,该模块将所有捆绑软件作为输出使用(应该制作较少的副本)。

我的PR还将chisel3和chisel-testers的依赖关系更改为SNAPSHOTS。

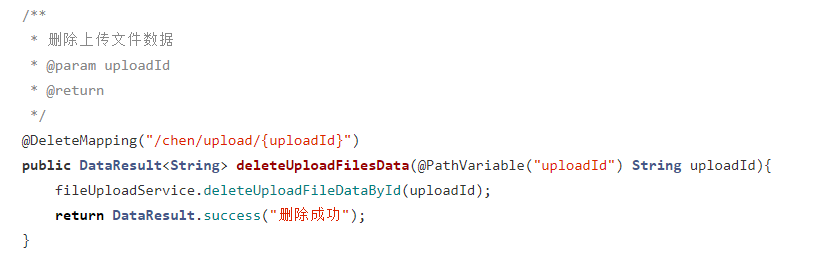

设置时间 控制面板

设置时间 控制面板 错误1:Request method ‘DELETE‘ not supported 错误还原:...

错误1:Request method ‘DELETE‘ not supported 错误还原:...